Preliminary data sheet

## 1. General description

NEX13120F-Q100 is an AEC-Q100 grade 1 qualified 12-channel, 40 V high-side LED driver with up to 100 mA output current per channel, PWM and analog dimming support, and MTP for configurable depending on application requirements in automotive lighting systems.

NEX13120F-Q100 supports 8-bit output current with high accuracy from channel to channel and device to device, channels can be used in parallel to support higher current output than 100 mA. The low dropout of the device helps to eliminate the heat generation of the device itself. The device integrates UART over CAN as the digital interface to enable long distance off-board communication, which is a typical scenario for automotive exterior lighting where different lamp functions are typically located in different PCB boards. NEX13120F-Q100 also supports LED open-circuit, short to ground, and single LED short-circuit diagnostics. Additionally, a configurable watchdog automatically sets the part into Fail-Safe states when the CAN bus connection is lost.

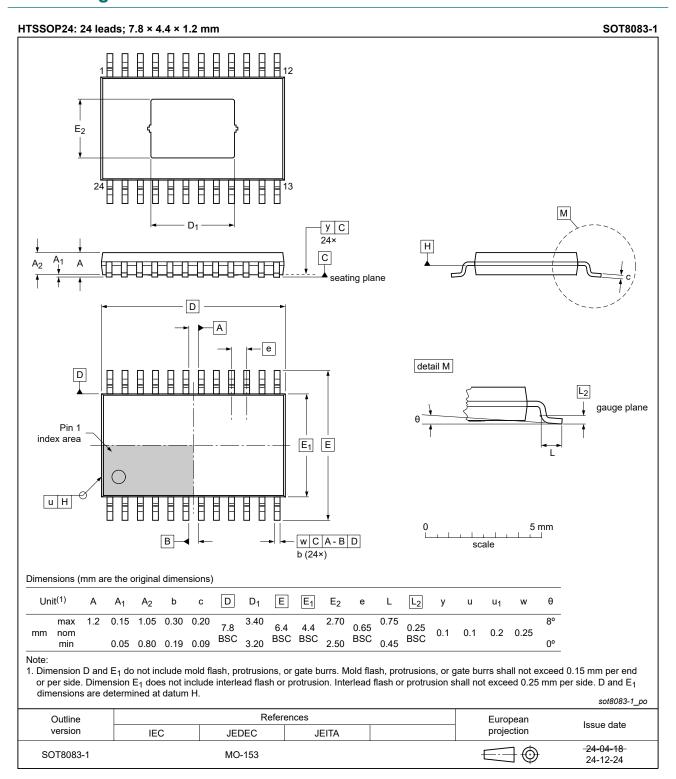

NEX13120F-Q100 can operate at a junction temperature range from -40 °C to +150 °C in a thermally enhanced 24-pin HTSSOP24 package.

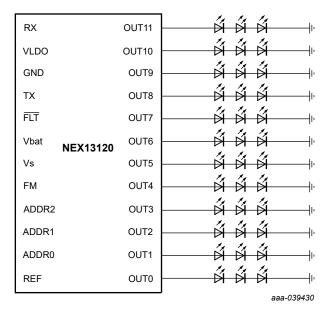

Fig. 1. Typical application

#### 2. Features and benefits

- AEC-Q100 qualified for automotive applications

- Specified from -40 °C to 125 °C

- Compliant with ISO 26262 and meets ASIL B requirements for functional safety

- 12-channel precision high-side current output:

- V<sub>bat</sub>: 4.5 V to 36 V and V<sub>s</sub>: 3.8 V to 36 V

- Up to 100 mA channel current per channel

- · 2-bit global, 6-bit independent current setting

- Current accuracy within ±5 % from 18 mA to 100 mA

- · Low voltage drops: 600 mV at 100 mA

- 12-bit independent PWM dimming

- Programmable PWM frequency: 50 Hz to 23.4 kHz

- · Linear and exponential dimming method

- Integrated UART interface:

- Data rate up to 2 Mbit/s

- Support UART data format

- · Support 27 slave address set by resistor

- Diagnostics and protections:

- Programmable FAIL-SAFE state

- · LED open-circuit detection

- · LED short-circuit detection

- · Single-LED short-circuit diagnostic

- Programmable low-V<sub>s</sub> detection

- Open-drain FLT pin for fault indication

- · Watchdog and CRC for data line

- MTP ECC check

- 8-bit ADC for pin voltage measurement

- · Over-temperature protection

- ESD protection:

- HBM: ANSI/ESDA/JEDEC JS-001 class 2 exceeds 2000 V

- CDM: ANSI/ESDA/JEDEC JS-002 class C2a exceeds 500 V

## 3. Applications

- Automotive exterior rear light

- · Automotive exterior headlight

# 4. Ordering information

## **Table 1. Ordering information**

| Type number      | Package           |      |                                                                                                   |           |

|------------------|-------------------|------|---------------------------------------------------------------------------------------------------|-----------|

|                  | Temperature range | Name | Description                                                                                       | Version   |

| NEX13120FPC-Q100 | -40 °C to +125 °C | _    | Thermal enhanced thin shrink small outline package; 24 leads; body size: 7.8 mm x 4.4 mm x 1.2 mm | SOT8083-1 |

# 5. Device comparison

## Table 2. Device comparison

| iable 2: 201100 companioon |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Type number                | Compliant safety standard                                                         |

| NEX13120PC-Q100            | Function safety capable Documents are provided to support function safety design. |

| NEX13120FPC-Q100           | Compliant with ISO 26262 and meets ASIL B requirements for functional safety      |

# 6. Marking

#### Table 3. Marking

| Type number      | Marking code |

|------------------|--------------|

| NEX13120PC-Q100  | N13120       |

| NEX13120FPC-Q100 | N13120F      |

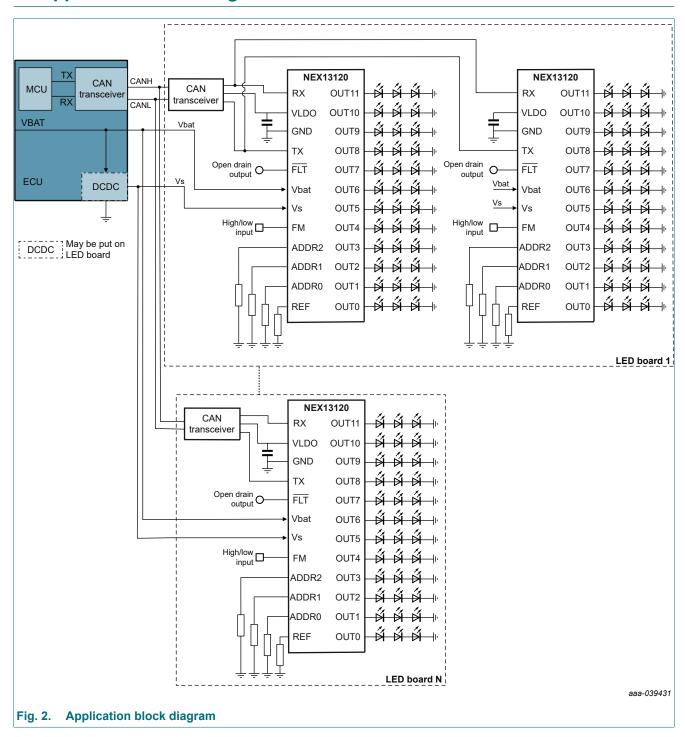

## 7. Application block diagram

# 8. Pinning information

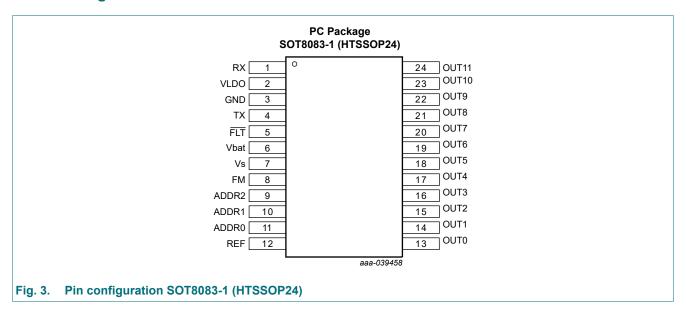

## 8.1. Pinning

## 8.2. Pin description

Table 4. Pin description

| Symbol           | Pin      | I/O   | Description                                                            |

|------------------|----------|-------|------------------------------------------------------------------------|

| RX               | 1        | I     | UART RX over CAN physical layer                                        |

| VLDO             | 2        | Power | output of internal 5 V LDO                                             |

| GND              | 3        | GND   | device ground                                                          |

| TX               | 4        | 0     | UART TX over CAN physical layer                                        |

| FLT              | 5        | I/O   | open-drain fault/error output                                          |

| V <sub>bat</sub> | 6        | Į     | power supply for internal circuit                                      |

| V <sub>s</sub>   | 7        | I     | power supply for current output channels                               |

| FM               | 8        | I     | Fail-Safe state selection  O: Fail-Safe mode 0  1: Fail-Safe mode 1    |

| ADDR2            | 9        | I     | device address 2                                                       |

| ADDR1            | 10       | I     | device address 1                                                       |

| ADDR0            | 11       | Į     | device address 0                                                       |

| REF              | 12       | I/O   | device reference current setting, MTP programming chip-selection input |

| OUT0 to OUT11    | 13 to 24 | 0     | current output channel 0 to 11                                         |

# 9. Limiting values

#### Table 5. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

| Symbol           | Parameter            | Conditions                                            | Min    | Max           | Unit |

|------------------|----------------------|-------------------------------------------------------|--------|---------------|------|

| VI               | input voltage        | pins V <sub>bat</sub> , V <sub>s</sub>                | - 0.3  | 45            | V    |

|                  |                      | pin REF, ADDRn                                        | - 0.3  | 5.5           | V    |

| Vo               | output voltage       | pins OUTn                                             | - 0.3  | $V_{s} + 0.3$ | V    |

|                  |                      | pin VLDO                                              | - 0.3  | 5.5           | V    |

| V <sub>I/O</sub> | I/O voltage          | pin FM                                                | - 0.3  | $V_{s} + 0.3$ | V    |

|                  |                      | pin FLT                                               |        | 22            | V    |

|                  |                      | pins RX, TX                                           | - 0.3  | 5.5           | V    |

| Tj               | junction temperature |                                                       | - 40   | 150           | °C   |

| T <sub>amb</sub> | ambient temperature  |                                                       | - 40   | 125           | °C   |

| T <sub>stg</sub> | storage temperature  |                                                       | - 65   | 150           | °C   |

| ESD              |                      |                                                       |        |               | •    |

| V <sub>ESD</sub> | ESD voltage          | Human Body Model (HBD) for all pins, per AEC Q100-002 | - 2000 | + 2000        | V    |

|                  |                      | Charged device model (CDM), per AEC Q100-011          |        |               |      |

|                  |                      | corner pins (1, 12, 13 and 24)                        | - 750  | + 750         | V    |

|                  |                      | all pins                                              | - 500  | + 500         | V    |

# 10. Recommended operating conditions

## Table 6. Recommended operating conditions

| Symbol                       | Parameter                        | Conditions                                                   | Min | Тур | Max | Unit |

|------------------------------|----------------------------------|--------------------------------------------------------------|-----|-----|-----|------|

| V <sub>I</sub> input voltage |                                  | pin V <sub>bat</sub> ; device supply voltage                 | 4.5 | -   | 36  | V    |

|                              |                                  | pin V <sub>s</sub> ; power supply for output current channel | 3.8 | -   | 36  | V    |

| Io                           | output current                   | pins OUTn; channel output current                            | -   | -   | 100 | mA   |

| VI                           | input voltage                    | pin FM; external Fail-Safe selection input                   | 0   | -   | Vs  | V    |

| V <sub>I/O</sub>             | input/output voltage             | pin TX; UART TX output                                       | 0   | -   | 5   | V    |

|                              |                                  | pin RX; UART RX input                                        | 0   | -   | 5   | V    |

| $V_{VLDO}$                   | VLDO voltage                     | pin VLDO; internal 5 V VLDO output                           | 0   | -   | 5   | V    |

| I <sub>VLDO</sub>            | VLDO current                     | pin VLDO; current capability                                 | 0   | -   | 80  | mA   |

| VI                           | input voltage                    | pins ADDRn; device address selection                         | 0   | -   | 5   | V    |

| V <sub>I/O</sub>             | input/output voltage             | pin REF; current reference setting                           | 0   | -   | 5   | V    |

|                              |                                  | pin FLT; fault/error feedback open-drain output              | 0   | -   | 20  | V    |

| F <sub>CLK</sub>             | UART baud rate                   |                                                              | 0.1 | -   | 2   | Mbps |

| D <sub>sync</sub>            | synchronization pulse duty cycle |                                                              | 45  | 50  | 55  | %    |

| Tj                           | junction temperature             |                                                              | -40 | -   | 150 | °C   |

| T <sub>amb</sub>             | ambient temperature              |                                                              | -40 | 25  | 125 | °C   |

## 11. Thermal information

#### **Table 7. Thermal information**

| Symbol                | Parameter                                 | SOT8083-1 | Unit |

|-----------------------|-------------------------------------------|-----------|------|

| $R_{\Theta JA}$       | junction-to-ambient thermal resistance    | 25.8      | °C/W |

| R <sub>OJC(TOP)</sub> | junction-to-case (top) thermal resistance | 29.2      | °C/W |

| R <sub>OJB</sub>      | junction-to-board thermal resistance      | 11.7      | °C/W |

| $\Psi_{JT}$           | junction-to-top char parameter            | 3.6       | °C/W |

## 12. Electrical characteristics

## **Table 8. Static characteristics**

At recommended operating conditions. Voltages are referenced to GND (ground = 0 V).

| Symbol                       | Parameter                                         | Conditions                                                                                                         | -40 ° | Unit |      |     |

|------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------|------|------|-----|

|                              |                                                   |                                                                                                                    | Min   | Тур  | Max  |     |

| Bias                         |                                                   |                                                                                                                    |       |      |      |     |

| V <sub>(Vbat)</sub>          | operating input voltage range                     |                                                                                                                    | 4.5   | 12   | 36   | V   |

| I <sub>q(Vbat)</sub>         | quiescent current, all-channels ON                | $V_{bat}$ = 12 V; $R_{REF}$ = 8.45 k $\Omega$ ;<br>all outputs ON; REFRANGE = 11b;<br>PWM duty = 0                 | -     | 8    | 9    | mA  |

|                              | quiescent current, all-channels OFF               | $V_{bat}$ = 12 V; $R_{REF}$ = 8.45 kΩ;<br>REFRANGE = 11b; all outputs OFF                                          | -     | 8    | 9    | mA  |

| I <sub>q(Vs)</sub>           | quiescent current, all-channels ON                | $V_{bat}$ = 12 V; $V_{s}$ = 12 V;<br>$R_{REF}$ = 8.45 k $\Omega$ ; REFRANGE = 11b;<br>PWM Duty = 0; all outputs ON | -     | 8    | -    | mA  |

|                              | quiescent current, all-channels-off               | $V_{bat}$ = 12 V; $V_{s}$ = 12 V; $R_{REF}$ = 8.45 k $\Omega$ ; REFRANGE = 11b; all outputs OFF                    | -     | 20   | 30   | μА  |

| I <sub>fault(Vbat)</sub>     | quiescent current, Fail-Safe state fault mode     | V <sub>s</sub> = 12 V; Fail-Safe state;<br>all outputs OFF; FLT = LOW                                              | -     | 8    | 9    | mA  |

| I <sub>fault(Vs)</sub>       | quiescent current, Fail-Safe state fault mode     | V <sub>s</sub> = 12 V; Fail-Safe state;<br>all outputs OFF;<br>FLT = LOW                                           | -     | 20   | 30   | μА  |

| I <sub>LKG(Vs)</sub>         | V <sub>s</sub> leakage current                    | V <sub>s</sub> = 36 V; V <sub>bat</sub> = 0 V                                                                      | -     | -    | 85   | μA  |

| V <sub>(Vbat_POR_rise)</sub> | V <sub>bat</sub> power-on-reset rising threshold  |                                                                                                                    | 4     | 4.2  | 4.45 | V   |

| V <sub>(Vbat_POR_fall)</sub> | V <sub>bat</sub> power-on-reset falling threshold |                                                                                                                    | 3.8   | 4    | 4.2  | V   |

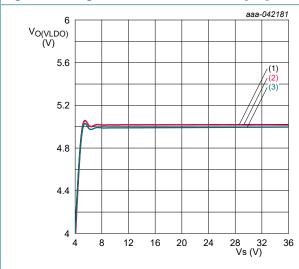

| V <sub>O(VLDO)</sub>         | VLDO output voltage                               | $V_{bat} > 5.6 \text{ V}; I_{(VLDO)} = 40 \text{ mA}$                                                              | 4.65  | 5    | 5.25 | V   |

| I <sub>O(VLDO)</sub>         | VLDO output current capability                    |                                                                                                                    | 80    | -    | -    | mA  |

| $I_{(VLDO\_limit)}$          | VLDO output current limit                         |                                                                                                                    | 110   | -    | -    | mA  |

| V <sub>(VLDO_POR_rise)</sub> | VLDO power-on-reset rising threshold              |                                                                                                                    | 2.75  | 3    | 3.25 | V   |

| $V_{(VLDO\_POR\_fall)}$      | VLDO power-on-reset falling threshold             |                                                                                                                    | 2.45  | 2.75 | 3    | V   |

| V <sub>(VLDO_OV_rise)</sub>  | VLDO overvoltage rising threshold [1]             |                                                                                                                    | -     | 5.7  | -    | V   |

| V <sub>(VLDO_OV_fall)</sub>  | VLDO overvoltage falling threshold [1]            |                                                                                                                    | -     | 5.5  | -    | V   |

| C <sub>VLDO</sub>            | supported VLDO loading capacitance                |                                                                                                                    | 1     | -    | 10   | μF  |

| f <sub>osc</sub>             | internal oscillator frequency                     |                                                                                                                    | -     | 24   | -    | MHz |

| Symbol                  | Parameter                                                                                             | Conditions                                                                                       | -40 ° | Unit |      |     |

|-------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------|------|------|-----|

|                         |                                                                                                       | Min                                                                                              | Тур   | Max  |      |     |

| FLT                     |                                                                                                       |                                                                                                  |       | •    |      |     |

| V <sub>IH(FLT)</sub>    | logic high voltage, FLT                                                                               |                                                                                                  | 2     | -    | -    | V   |

| V <sub>IL(FLT)</sub>    | logic low voltage, FLT                                                                                |                                                                                                  | -     | -    | 0.7  | V   |

| I <sub>pd(FLT)</sub>    | FLT pull-down current capability                                                                      | V <sub>(FLT)</sub> = 0.4 V                                                                       | 3     | 5.5  | 9    | mA  |

| I <sub>LKG(FLT)</sub>   | FLT leakage current                                                                                   | V <sub>(FLT)</sub> = 5 V                                                                         | -     | -    | 1    | μA  |

| UART interfa            | ace                                                                                                   |                                                                                                  |       |      |      |     |

| $V_{IL(RX)}$            | input logic low voltage, RX                                                                           |                                                                                                  | -     | -    | 0.7  | V   |

| $V_{IH(RX)}$            | input logic high voltage, RX                                                                          |                                                                                                  | 2     | -    | -    | V   |

| $V_{OL(TX)}$            | low-level output voltage TX,                                                                          | I <sub>sink</sub> = 5 mA                                                                         | 0     | -    | 0.47 | V   |

| $V_{OH(TX)}$            | high-level output voltage TX,                                                                         | I <sub>source</sub> = 5 mA; V <sub>pull-up</sub> = 5 V                                           | 4.5   | -    | 5    | V   |

| I <sub>LKG(TX-RX)</sub> | TX, RX leakage current                                                                                | V <sub>RX</sub> = 5 V; V <sub>TX</sub> = 5 V                                                     | -1    | -    | 1    | μA  |

| ADDRESS, F              | FS .                                                                                                  |                                                                                                  |       |      |      |     |

| V <sub>IL(FS)</sub>     | input logic low voltage, FS                                                                           |                                                                                                  | -     | -    | 0.7  | V   |

| V <sub>IH(FS)</sub>     | input logic high voltage, FS                                                                          |                                                                                                  | 2     | -    | -    | V   |

| $V_{IL(ADDRn)}$         | logic low voltage<br>ADDR2, ADDR1, ADDR0                                                              |                                                                                                  | -     | -    | 0.7  | V   |

| V <sub>IM(ADDRn)</sub>  | middle logic voltage<br>ADDR2, ADDR1, ADDR0                                                           |                                                                                                  | 0.86  | -    | 1.6  | V   |

| $V_{IH(ADDRn)}$         | logic high voltage<br>ADDR2, ADDR1, ADDR0                                                             |                                                                                                  | 2     | -    | -    | V   |

| R <sub>PD(FS)</sub>     | internal pull-down resistance, FS                                                                     |                                                                                                  | -     | 100  | -    | kΩ  |

| ADC[1]                  |                                                                                                       |                                                                                                  |       |      |      |     |

| DNL                     | differential non linearity                                                                            |                                                                                                  | -1    | -    | 1    | LSB |

| INL                     | differential non linearity                                                                            |                                                                                                  | -2    | -    | 2    | LSB |

| OUTPUT DR               | RIVERS                                                                                                |                                                                                                  |       |      |      |     |

| f <sub>PWM</sub>        | PWM dimming frequency range                                                                           | CONF_PWMSLOW = 0                                                                                 | 0.2   | -    | 25.3 | kHz |

|                         |                                                                                                       | CONF_PWMSLOW = 1                                                                                 | 0.05  | -    | 5.86 | kHz |

| $\Delta I_{(OUT\_d2d)}$ | device-to-device accuracy<br>ΔI <sub>(OUT_d2d)</sub> = 1-I <sub>avg(OUT)</sub> /I <sub>nom(OUT)</sub> | $R_{REF}$ = 6.34 k $\Omega$ ; REFRANGE = 11b; DC = 63; $I_{OUT}$ = 100 mA                        | -5    | 0    | 5    | %   |

|                         |                                                                                                       | $R_{REF}$ = 8.45 k $\Omega$ ; REFRANGE = 11b; DC = 63; $I_{OUT}$ = 75 mA                         | -5    | 0    | 5    | %   |

|                         |                                                                                                       | $R_{(REF)} = 8.45 \text{ k}\Omega;$<br>REFRANGE = 10b;<br>DC = 63; $I_{OUT}$ = 37.5 mA           | -5    | 0    | 5    | %   |

|                         |                                                                                                       | $R_{REF} = 8.45 \text{ k}\Omega; \text{ REFRANGE} = 01b; \\ DC = 63; I_{OUT} = 18.75 \text{ mA}$ | -6    | 0    | 6    | %   |

| $\Delta I_{(OUT\_c2c)}$ | channel-to-channel accuracy $\Delta I_{(OUT_{c}2c)} = 1 - I_{(OUT_{n})}/I_{avg(OUT)}$                 | $R_{REF}$ = 6.34 k $\Omega$ ; REFRANGE = 11b; DC = 63; $I_{OUT}$ = 100 mA                        | -5    | 0    | 5    | %   |

|                         |                                                                                                       | $R_{REF}$ = 8.45 k $\Omega$ ; REFRANGE = 11b; DC = 63; $I_{OUT}$ = 75 mA                         | -5    | 0    | 5    | %   |

|                         |                                                                                                       | $R_{REF}$ = 8.45 k $\Omega$ ; REFRANGE = 10b; DC = 63; $I_{OUT}$ = 37.5 mA                       | -5    | 0    | 5    | %   |

|                         |                                                                                                       | $R_{REF} = 8.45 \text{ k}\Omega; \text{ REFRANGE} = 01b; \\ DC = 63; I_{OUT} = 18.75 \text{ mA}$ | -6    | 0    | 6    | %   |

| Symbol                      | Parameter                                     | Conditions                                                                | -40 ° | Unit    |     |    |

|-----------------------------|-----------------------------------------------|---------------------------------------------------------------------------|-------|---------|-----|----|

|                             |                                               |                                                                           | Min   | Тур Мах |     | 1  |

| $V_{(OUT\_drop)}$           | output dropout voltage                        | $R_{REF}$ = 8.45 k $\Omega$ ; REFRANGE = 11b; DC = 38; $I_{OUT}$ = 45 mA  | 300   | 430     | 590 | mV |

|                             |                                               | $R_{REF}$ = 8.45 k $\Omega$ ; REFRANGE = 11b; DC = 63; $I_{OUT}$ = 75 mA  | 360   | 490     | 730 | mV |

|                             |                                               | $R_{REF}$ = 6.34 k $\Omega$ ; REFRANGE = 11b; DC = 63; $I_{OUT}$ = 100 mA | 400   | 600     | 860 | mV |

| R <sub>REF</sub>            |                                               |                                                                           | 5     | -       | 50  | kΩ |

| C <sub>REF</sub>            |                                               |                                                                           | 0     | -       | 4.7 | nF |

| V <sub>REF</sub>            |                                               |                                                                           | -     | 1.235   | -   | V  |

| K <sub>(REF_11)</sub>       |                                               | REFRANGE = 11b                                                            | -     | 512     | -   | -  |

| K <sub>(REF_10)</sub>       |                                               | REFRANGE = 10b                                                            | -     | 256     | -   | -  |

| K <sub>(REF_01)</sub>       |                                               | REFRANGE = 01b                                                            | -     | 128     | -   | -  |

| K <sub>(REF_00)</sub>       |                                               | REFRANGE = 00b                                                            | -     | 64      | -   | -  |

| I <sub>(REF_OPEN_th)</sub>  |                                               |                                                                           | 4     | 12      | 20  | μA |

| V <sub>(REF_SHORT_th)</sub> |                                               |                                                                           | 0.4   | 0.6     | 0.8 | V  |

| DIAGNOSTICS                 |                                               |                                                                           |       |         |     |    |

| V <sub>(Vs_th_rise)</sub>   | V <sub>s</sub> undervoltage rising threshold  |                                                                           | 2.5   | 2.75    | 2.9 | V  |

| V <sub>(Vs_th_fall)</sub>   | V <sub>s</sub> undervoltage falling threshold |                                                                           | 2.3   | 2.55    | 2.7 | V  |

| V <sub>(Vs_th_hyst)</sub>   | V <sub>s</sub> undervoltage hysteresis        |                                                                           | -     | 200     | -   | mV |

| V <sub>(OPEN_th_rise)</sub> | LED open rising threshold,<br>AUTOSS = 0      | V <sub>(Vs)</sub> - V <sub>(OUTn)</sub>                                   | 200   | 240     | 325 | mV |

| V <sub>(OPEN_th_rise)</sub> | LED open rising threshold,<br>AUTOSS = 1      | V <sub>(Vs)</sub> - V <sub>(OUTn)</sub>                                   | 230   | 300     | 445 | mV |

| V <sub>(OPEN_th_fall)</sub> | LED open falling threshold                    | V <sub>(Vs)</sub> - V <sub>(OUTn)</sub>                                   | 140   | 400     | 450 | mV |

| V <sub>(OPEN_th_hyst)</sub> | LED open hysteresis                           |                                                                           | -     | 100     | -   | mV |

| V <sub>(SG_th_rise)</sub>   | short to GND rising threshold                 |                                                                           | 0.8   | 0.9     | 1   | V  |

| V <sub>(SG_th_fall)</sub>   | short to GND falling threshold                |                                                                           | 1.05  | 1.2     | 1.3 | V  |

| V <sub>(SG_th_hyst)</sub>   | short to GND hysteresis                       |                                                                           | -     | 0.3     | -   | V  |

| MTP                         |                                               |                                                                           |       |         |     |    |

| N <sub>(MTP)</sub>          | number of programming cycles                  | VLDO = 5 V                                                                | 1000  | -       | -   | -  |

| Temperature[1               | 1                                             |                                                                           |       |         |     |    |

| T <sub>(PRETSD)</sub>       | pre-thermal warning threshold                 |                                                                           | -     | 135     | -   | °C |

| T <sub>(PRETSD_HYS)</sub>   | pre-thermal warning hysteresis                |                                                                           | -     | 5       | -   | °C |

| T <sub>(TSD1)</sub>         | over-temperature protection threshold         |                                                                           | -     | 175     | -   | °C |

| T <sub>(TSD2)</sub>         | over-temperature shutdown threshold           |                                                                           | -     | 185     | -   | °C |

| T <sub>(TSD1_HYS)</sub>     | over-temperature protection hysteresis        |                                                                           | -     | 15      | -   | °C |

| T <sub>(TSD2_HYS)</sub>     | over-temperature shutdown hysteresis          |                                                                           | -     | 15      | -   | °C |

<sup>[1]</sup> Guaranteed by bench test, not fully tested in production.

**Table 9. Timing requirement**

| Symbol               | Parameter                                 | Conditions | -40 ° | Unit |     |    |

|----------------------|-------------------------------------------|------------|-------|------|-----|----|

|                      |                                           |            | Min   | Тур  | Max |    |

| t <sub>(ODPW)</sub>  | diagnostics pulse-width, ODPW = 0h        |            | -     | 100  | -   | μs |

| t <sub>(CONV)</sub>  | time needed to complete one AD conversion |            | -     | 55   | -   | μs |

| t <sub>(retry)</sub> | fault retry timer                         |            | -     | 10   | -   | ms |

# 13. Typical characteristics

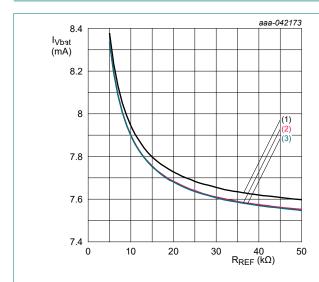

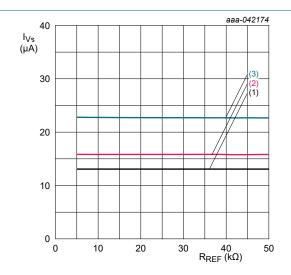

CONF\_REFRANGE[1:0] = 3h

(1)

$$T_{amb} = -40$$

°C

(1)  $T_{amb} = 125 \, ^{\circ}C$

CONF\_REFRANGE[1:0] = 3h

(1)

$$T_{amb} = -40 \, ^{\circ}C$$

(2)

$$T_{amb}$$

= 25 °C

(3)

$$T_{amb} = 125 \, ^{\circ}C$$

Fig. 5. V<sub>s</sub> standby current versus R<sub>REF</sub> resistor

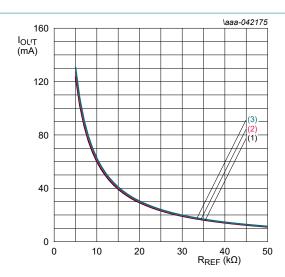

CONF\_IOUTx[5:0] = 3Fh CONF\_REFRANGE[1:0] = 3h

(1)  $T_{amb} = -40 \, ^{\circ}C$

(2)  $T_{amb} = 25 \, ^{\circ}C$

(3)  $T_{amb}$  = 125 °C

CONF\_REFRANGE[1:0] = 3h

(1)  $I_{OUT} = 100 \text{ mA}$

(2)  $I_{OUT} = 75 \text{ mA}$

(3)  $I_{OUT} = 50 \text{ mA}$

(4)  $I_{OUT} = 5 \text{ mA}$

Fig. 6. Output full-range current versus R<sub>REF</sub> resistor

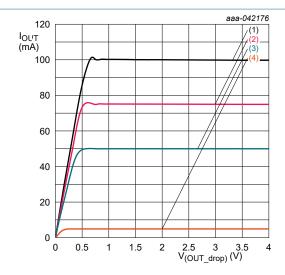

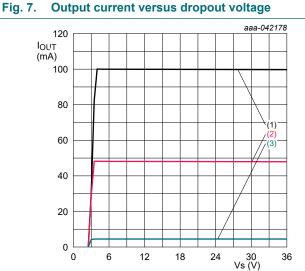

$R_{REF}$  = 6.34  $k\Omega$  & 12.6  $k\Omega$

CONF\_REFRANGE[1:0] = 3h

(1)  $I_{OUT}$  = 100 mA;  $T_{amb}$  = 125 °C

(2)  $I_{OUT} = 100 \text{ mA}$ ;  $T_{amb} = 25 ^{\circ}\text{C}$

(3)  $I_{OUT} = 100 \text{ mA}$ ;  $T_{amb} = -40 \, ^{\circ}\text{C}$

(4)  $I_{OUT} = 50 \text{ mA}$ ;  $T_{amb} = 125 ^{\circ}\text{C}$

(5)  $I_{OUT}$  = 50 mA;  $T_{amb}$  = -40 °C

(6)  $I_{OUT} = 50 \text{ mA}$ ;  $T_{amb} = 25 ^{\circ}\text{C}$

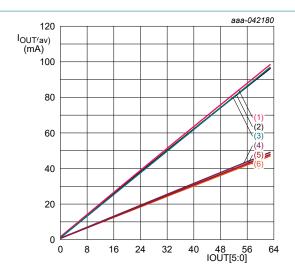

Fig. 8. Output current versus dropout voltage

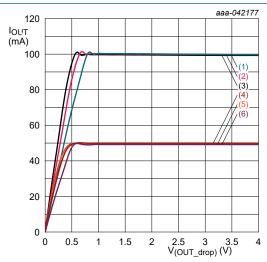

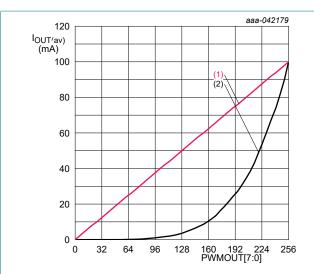

CONF\_REFRANGE[1:0] = 3h

(1)  $I_{OUT} = 100 \text{ mA}$

(2)  $I_{OUT} = 50 \text{ mA}$

(3)  $I_{OUT} = 5 \text{ mA}$

Fig. 9. Output current versus dropout voltage

CONF\_EXPEN = 0 & 1 CONF\_IOUTx[5:0] = 3Fh

(1) CONF\_EXPEN = 0

(2) CONF\_EXPEN = 1

$R_{REF}$  = 6.34  $k\Omega$  & 12.6  $k\Omega$

CONF\_REFRANGE[1:0] = 3h

(1)  $I_{OUT} = 100 \text{ mA}$ ;  $T_{amb} = 25 ^{\circ}\text{C}$

(2)  $I_{OUT} = 100 \text{ mA}$ ;  $T_{amb} = -40 ^{\circ}\text{C}$

(3)  $I_{OUT}$  = 100 mA;  $T_{amb}$  = 125 °C

(4)  $I_{OUT}$  = 50 mA;  $T_{amb}$  = 125 °C

(5)  $I_{OUT} = 50 \text{ mA}$ ;  $T_{amb} = 25 \text{ °C}$

(6)  $I_{OUT} = 50 \text{ mA}$ ;  $T_{amb} = -40 ^{\circ}\text{C}$

Fig. 10. Average current versus PWMOUT[7:0]

(1)  $T_{amb} = -40 \, ^{\circ}C$

(2)  $T_{amb} = 25 \, ^{\circ}C$

(3) T<sub>amb</sub> = 125 °C

Fig. 12. LDO output line regulation

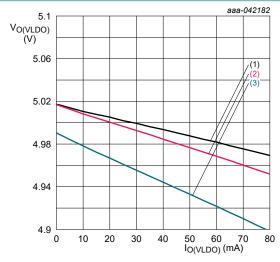

(1)  $T_{amb} = -40 \, ^{\circ}C$

(2)  $T_{amb} = 25 \, ^{\circ}C$

(3)  $T_{amb} = 125 \, ^{\circ}C$

Fig. 13. LDO output load regulation

## 14. Detailed description

#### 14.1. Overview

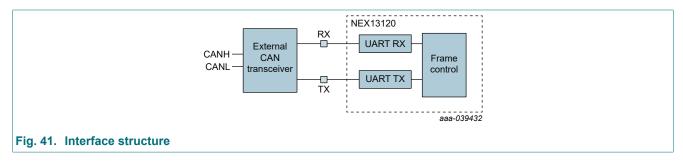

The NEX13120F-Q100 is an automotive 12-channel LED driver equipped with a UART interface to meet the growing demand for individual control of each LED string. Each channel supports both analog dimming and PWM dimming, configurable via the UART. The internal MTP memory enables users to set configurations in the event of communication loss, ensuring compliance with system-level safety requirements.

The integrated UART interface is compliant with physical layer transceiver such as CAN or LIN transceivers. It can support off-board communication with the transition of CAN or LIN transceivers.

Each output channel serves as a constant current source, allowing for individually programmable current outputs and PWM duty cycles. The device includes various diagnostic features, such as LED open-circuit, short-circuit, and single-LED short-circuit detection. Additionally, the on-chip ADC enables real-time monitoring of output conditions.

To enhance robustness, NEX13120F-Q100 integrates Fail-Safe state machine that automatically switches to Fail-Safe states in case of communication loss, such as MCU failure. Users can program Fail-Safe settings using the MTP, allowing for different configurations in the event of output failure, such as one-fails-all-fail or one-fails-others-on. Each channel can be independently programmed to either remain on or off during Fail-Safe states.

The Fail-Safe state machine also permits the system to operate with pre-programmed MTP settings without the presence of a controller, enabling stand-alone operation. The micro-controller can access each device through the UART interface, allowing full control over the device and LEDs by setting and reading back registers. All MTPs are pre-programmed with default values, and it is recommended for the users to program the MTP at the end of the production line for application-specific settings and Fail-Safe configurations.

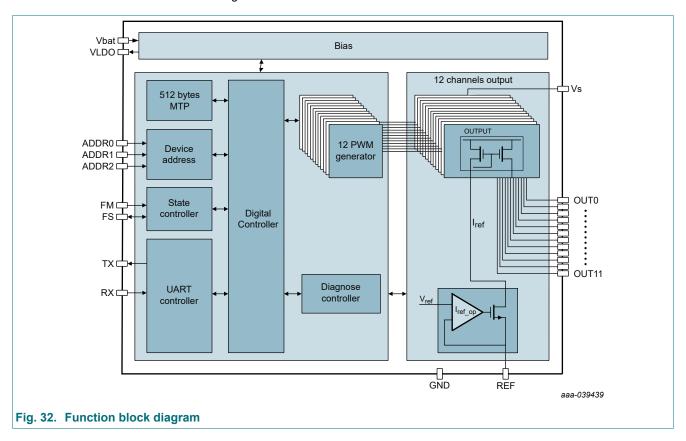

## 14.2. Function block diagram

The NEX13120F-Q100 function block diagram is shown below:

## 14.3. Feature description

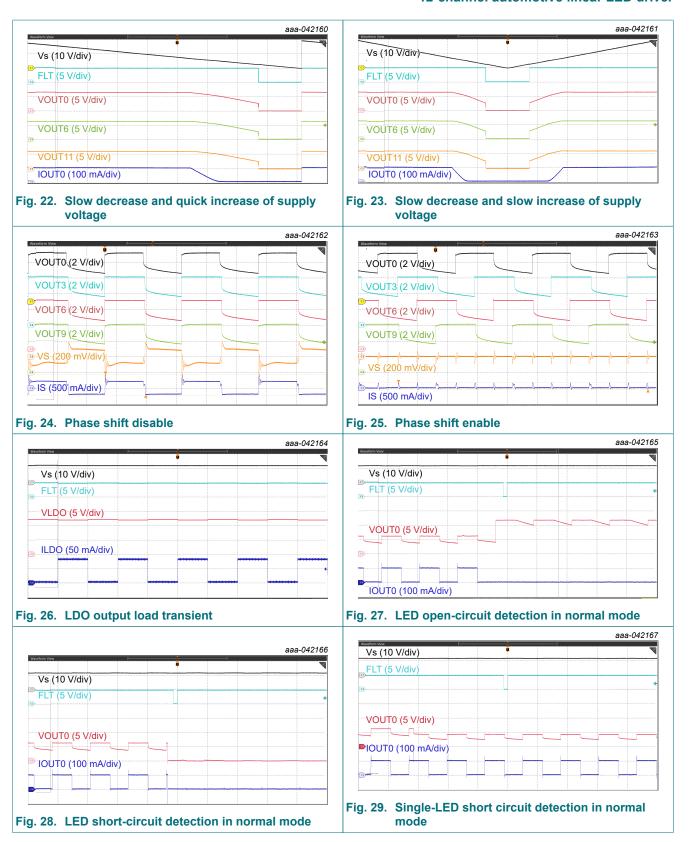

## 14.3.1. Device bias and power

#### Power supply (V<sub>bat</sub>)

The NEX13120F-Q100 is AEC Q-100 qualified for automotive applications. The power input to the device through  $V_{bat}$  pin can be low to 4.5 V and up to 36 V for automotive battery directly powered systems. All the internal analog and digital circuits except for the current output channels are powered by  $V_{bat}$ .

## 5 V low drop-out linear regulator (VLDO)

NEX13120F-Q100 has an integrated low-drop-out linear regulator to provide power supply to external CAN transceivers. The internal LDO powered by input voltage  $V_{(Vbat)}$  provides a stable 5 V output with up to 80 mA constant current capability. It is recommended to use a ceramic capacitor from 1  $\mu$ F to 10  $\mu$ F on the VLDO pin. The LDO has an internal current limit  $I_{(VLDO\_limit)}$  for protection and soft start. The capacitor charging time must be considered to total start-up time because the device is held in POR state if the capacitor voltage is not charged to above UVLO threshold.

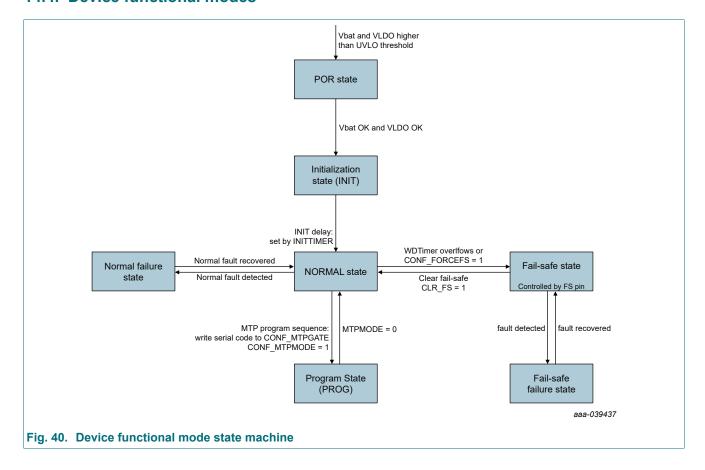

## Under-voltage lockout (UVLO) and power-on-reset (POR)

NEX13120F-Q100 uses UVLO and POR circuitry to clear its internal registers upon power-up and to reset registers with its default values. NEX13120F-Q100 has internal UVLO circuits so that when either input voltage  $V_{(Vbat)}$  or LDO output voltage  $V_{(VLDO)}$  is lower than its UVLO threshold, POR is triggered. In POR state, the device resets digital core and all registers to default value. FLAG\_POR and FLAG\_ERR register are set to 1 for each POR cycle to indicate the POR history. Before both powers are above UVLO thresholds, NEX13120F-Q100 stays in POR state with all outputs off and FLT pin pulled down.

Once both power supplies are above UVLO threshold, the device enters INIT mode for initialization releasing FLT pin pull-down. A programmable timer starts counting in INIT state, the timer length can be set by MTP register NV\_INITTIMER. When the timer has expired, the device switches to NORMAL state. In INIT state, setting CLR\_POR to 1 clears FLAG\_POR, disables the timer, and sets the device to NORMAL state. Upon powering up, NEX13120F-Q100 automatically loads all the settings stored in MTP to correlated registers and sets the other registers to default value which do not have correlated MTP. All channels are powered up off-state by default to avoid unwanted blinking. Writing 1 to CLR\_REG manually loads MTP setting to the correlated registers and set the other registers to default value. After CLR\_REG is set, the FLAG\_POR is cleared to 0.

Writing 1 to CLR\_POR also resets the FLAG\_POR register to 0. It is recommended to set CLR\_REG to 1 to clear the internal registers every time after POR. The CLR\_REG automatically resets to 0.

## Power supply (V<sub>s</sub>)

NEX13120F-Q100 has additional  $V_s$  input pins for powering all 12 high-side current output channels. The  $V_s$  voltage can be low to 3.8 V and up to 36 V for either automotive battery directly powered systems or an external DC-to-DC converter output. An external DC-to-DC converter can provide a regulated voltage for required LED output forward voltage from wide automotive battery voltage range.

NEX13120F-Q100 has an internal under-voltage detection circuit for  $V_s$  input. When the  $V_s$  input voltage is lower than under-voltage threshold,  $V_{(Vs\_th\_fall)}$ , all 12 current output channels are disabled with  $\overline{FLT}$  pin constantly pulled low and register flags set to 1 including FLAG\_ERR bit and FLAG\_VSUV bit. Table 17 shows the detailed fault behavior in NORMAL state.

## Programmable low V<sub>s</sub> supply warning

NEX13120F-Q100 uses its internal ADC to monitor supply voltage  $V_s$ . If the  $V_s$  is below allowable working threshold, the output voltage can be insufficient to keep the LED operating with the desired brightness output as expected. The  $V_s$  voltage is automatically compared with the threshold set by register CONF\_ADCLOWVSTH. When the  $V_s$  voltage is below the threshold, the device sets the warning flag register FLAG\_LOWVS and FLAG\_ERR to 1 in the status register. CLR\_ERR can clear the FLAG\_LOWVS as well as other fault registers. Low- $V_s$  warning clears LED open and single-LED short faults. In addition, the LED open-circuit and single LED short-circuit detection is disabled if the  $V_s$  voltage is below threshold to avoid the LED open circuit and to prevent the single LED short-circuit fault from being mis-triggered. The 4-bit register CONF\_ADCLOWVSTH has 16 options covering from 4 V to 19 V as shown below.

Table 10. Low supply warning threshold setting

| CONF_ADCLOWVSTH | 0h | 1h | 2h | 3h | 4h | 5h | 6h | 7h | 8h | 9h | Ah | Bh | Ch | Dh | Eh | Fh |

|-----------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Voltage (V)     | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 4  |

#### 14.3.2. Constant current output

## Constant current output reference current with external resistor (R<sub>REF</sub>)

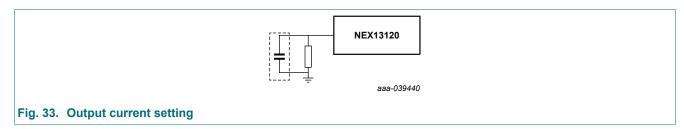

The NEX13120F-Q100 must have an external resistor R<sub>REF</sub> to set the internal current reference I<sub>REF</sub> as shown in Fig. 33.

The internal current reference,  $I_{(FULL\_RANGE)}$ , is generated based on the  $I_{REF}$  multiplied by factor  $K_{(REF)}$  to provide the full range current reference for each OUTx channel. The  $K_{REF}$  is programmable by 2-bit register CONF\_REFRANGE with four different options. Use the following equation to calculate the  $I_{(full\_range)}$ :

$$I_{\text{full\_range}} = \frac{V_{\text{REF}}}{R_{\text{REF}}} \cdot K_{\text{REF}}$$

(1)

NEX13120F\_Q100

All information provided in this document is subject to legal disclaimers

© Nexperia B.V. 2025. All rights reserved

Where V<sub>REF</sub> = 1.235 V, K<sub>REF</sub> = 64, 128, 256 or 512 (default)

Table 11. Reference current range setting

| Reference | K <sub>REF</sub> | Full range current (mA)    |                                  |                            |                            |  |  |  |

|-----------|------------------|----------------------------|----------------------------------|----------------------------|----------------------------|--|--|--|

|           |                  | R <sub>REF</sub> = 6.34 kΩ | $R_{REF} = 8.45 \text{ k}\Omega$ | $R_{REF}$ = 12.7 $k\Omega$ | R <sub>REF</sub> = 31.6 kΩ |  |  |  |

| 11b       | 512              | 100                        | 75                               | 50                         | 20                         |  |  |  |

| 10b       | 256              | 50                         | 37.5                             | 25                         | 10                         |  |  |  |

| 01b       | 128              | 25                         | 18.75                            | 12.5                       | 5                          |  |  |  |

| 00b       | 64               | 12.5                       | 9.375                            | 6.25                       | 2.5                        |  |  |  |

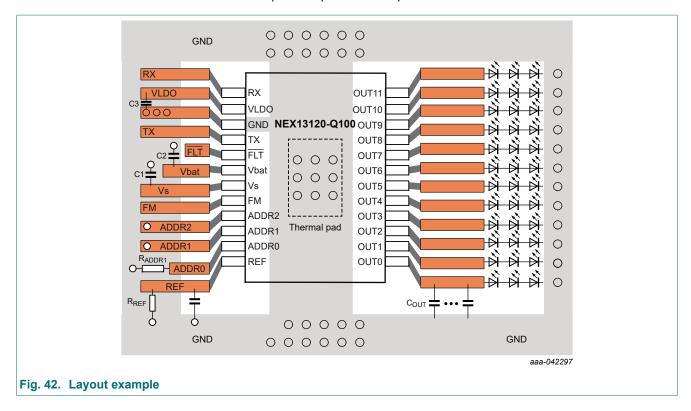

It is recommended to place the  $R_{REF}$  resistor as close as possible to the REF pin with a ceramic capacitor (up to 2.2 nF) in parallel to improve the noise immunity. It is also recommended to use a 1 nF ceramic capacitor in parallel with  $R_{REF}$ .

## 64-step programmable high-side constant-current output

NEX13120F-Q100 has 12 channels of high-side current sources. Each channel has its own enable configuration register CONF\_ENCHn. Setting CONF\_ENCHn to 1 enables the channel output, clearing the register to 0 disables the channel output. To completely turn off the channel current, user can clear channel enable bit CONF\_ENCHn to 0. Upon powering up, CONF\_ENCHn is automatically reset to 0 to avoid unwanted blinking.

Each OUTn channel supports individual 64-step programmable current setting, also known as Dot Correction (DC). The DC feature can be used to set binning values for output LEDs or to calibrate the LEDs to achieve high brightness homogeneity based on external visual system to further save binning cost. The 6-bit register CONF\_IOUTn sets the current independently, where n is the channel number from 0 to 11. The OUTn current can be calculated with the equation below:

$$I_{OUTn} = \frac{(CONF\_IOUTn+1)}{64} \times I_{full\_range}$$

(2)

## Where:

- CONF IOUTn is programmable from 0 to 63

- n is from 0 to 11 for different output channel

- I<sub>(full range)</sub> can be calculated with equation (1)

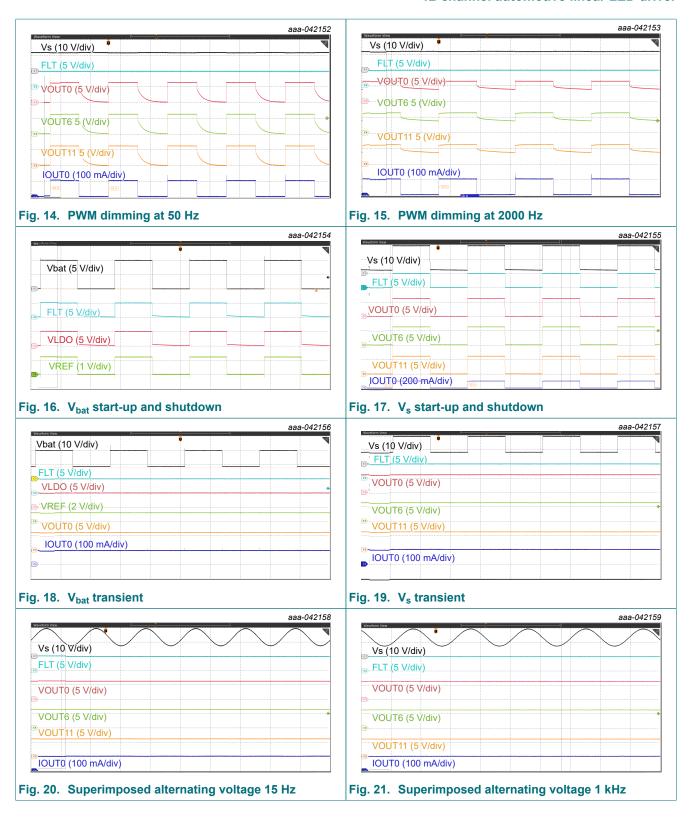

## 14.3.3. PWM dimming

NEX13120F-Q100 integrates independent 12-bit PWM generators for each OUTn channel. The integrated PWM generator turns the current output for each OUTn channel on and off. The average current of each OUTn can be adjusted by PWM duty cycle independently, therefore, to control the brightness for LEDs in each channel.

## **PWM** dimming frequency

The frequency for PWM dimming is programmable by 4-bit register CONF\_PWMFREQ and register CONF\_PWMSLOW with 32 options covering from 50 Hz to 23.4 kHz. CONF\_PWMSLOW default value is 0, it supports 200 Hz to 23.4 kHz; when set CONF\_PWMSLOW to 1, it supports lower PWM frequency, the range is 50 Hz to 5.86 kHz. Select the frequency for PWM dimming based on the minimum brightness requirement in application. NEX13120F-Q100 supports down to 1 µs minimum pulse current for all 12 channel outputs.

Below is the frequency table:

Table 12. PWM frequency setting

| PWM frequency setting | PWM cycle        | frequency        |  |  |

|-----------------------|------------------|------------------|--|--|

| CONF_PWMFREQ          | CONF_PWMSLOW = 0 | CONF_PWMSLOW = 1 |  |  |

| 0                     | 200              | 50               |  |  |

| 1                     | 250              | 60               |  |  |

| 2                     | 300              | 75               |  |  |

| 3                     | 350              | 90               |  |  |

| 4                     | 400              | 100              |  |  |

| 5                     | 500              | 125              |  |  |

| 6                     | 600              | 150              |  |  |

| 7                     | 800              | 200              |  |  |

| 8                     | 1000             | 250              |  |  |

| 9                     | 1200             | 300              |  |  |

| 10                    | 2000             | 500              |  |  |

| 11                    | 4000             | 1000             |  |  |

| 12                    | 5800             | 1500             |  |  |

| 13                    | 7800             | 2000             |  |  |

| 14                    | 9400             | 2300             |  |  |

| 15                    | 23400            | 5800             |  |  |

#### **ODPW** time

As NEX13120F-Q100 supports PWM control for adjusting LED brightness, the voltage on OUTn is like a pulse waveform. The output voltage and current ramp up to the target value in a certain period of time after the channel is turned on, depending on the value of capacitor on the OUTn pin. The ramping up period is proportional to the capacitance value of the capacitor. To avoid the output voltage of each OUTn is measured in the ramping up transient period, NEX13120F-Q100 integrates a t<sub>(ODPW)</sub> timer which is programmable by a 4-bit register CONF\_ODPW to setup the ODPW time for all OUTn. The device does not start the OUTn diagnostics and ADC measurement until the t<sub>(ODPW)</sub> timer is overflow. The t<sub>(ODPW)</sub> timer is programmable from 20 µs to 5 ms as described in Table 13. It is recommended to set t<sub>(ODPW)</sub> less than the PWM dimming period which is programmable by CONF\_PWMFREQ register, otherwise the OUTn diagnostics and ADC measurement only operates properly when PWM duty cycle is set to 100 %.

Table 13. ODPW time setting

|                          |      | ODPW time |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

|--------------------------|------|-----------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Binary code              | 0000 | 0001      | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

| T <sub>(ODPW)</sub> (µs) | 100  | 20        | 30   | 50   | 80   | 150  | 200  | 300  | 500  | 800  | 1000 | 1200 | 1500 | 2000 | 3000 | 5000 |

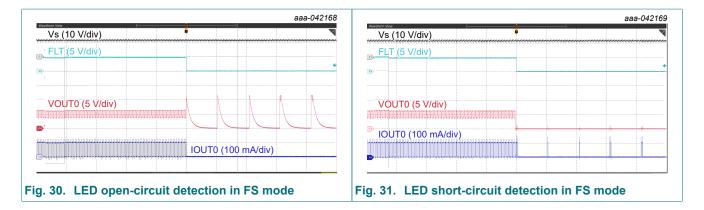

#### **Phase shift PWM dimming**

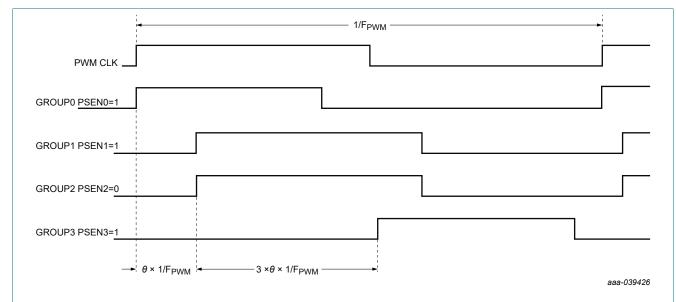

If all 12 output channels start PWM period at the same time, the peak output current of the chip is high. To reduce the peak current of the chip, the user can configure a phase shift. In phase shift PWM dimming mode, every three current output channels are formed as one group, one group phase is same and its phase is controlled by NV\_PS $\theta$ [1:0]. In case the phase shift is enabled, Group[x] turns on with a delay of T $\theta$ =X ×  $\theta$  × 1/FPWM, where X = 0 to 4. In case the phase shift is disabled, Group[x] turns on simultaneously with Group[x-1]. Both cases are shown in Fig. 34. When CONF\_PSENx is set to 1, Group[x] phase shift is enabled. Setting CONF\_PSENx to 0 can disable phase shift for Group[x].  $\theta$  is configurable by register CONF\_PS $\theta$ [1:0],  $\theta$  is a ratio parameter of 1/FPWM, FPWM is configured by CONF\_PWMFREQ.

| Group  | Outputs            | CONF_PS0 | Description                              |

|--------|--------------------|----------|------------------------------------------|

| GROUP0 | OUT0, OUT1, OUT2   | 0        | Delay time is 1/4 of 1/F <sub>PWM</sub>  |

| GROUP1 | OUT3, OUT4, OUT5   | 1        | Delay time is 1/6 of 1/F <sub>PWM</sub>  |

| GROUP2 | OUT6, OUT7, OUT8   | 2        | Delay time is 1/8 of 1/F <sub>PWM</sub>  |

| GROUP3 | OUT9, OUT10, OUT11 | 3        | Delay time is 1/12 of 1/F <sub>PWM</sub> |

Fig. 34. PWM phase shift

### **Linear brightness control**

When register CONF\_EXPEN is set to 0, the MSB 8 bits of 12-bit binary input to PWM generator are directly copied from 8-bit register CONF\_PWMOUTn, and the LSB 4 bits are directly copied from 4-bit register CONF\_PWMLOWOUTn. The PWM output duty cycle can be calculated with the following equation:

$$D_{OUTn} = \frac{(16 \times PWMOUTn + PWMLOWOUTn + 1)}{4096} \times 100\%$$

(3)

Where:

PWMOUTn is decimal number from 0 to 255 PWMLOWOUTn is decimal number from 0 to 15 n is from 0 to 11

The PWM output duty cycle is linearly controlled by the register CONF\_PWMOUTn and CONF\_PWMLOWOUTn, which provides linear brightness control to each channel output. When CONF\_PWMOUTn is 00h, and CONF\_PWMLOWOUTn is 0h, the channel turns off.

As 12-bit PWM duty cycles require 2 bytes of write operation to update the completed data, the output PWM duty cycle is not changed in between of the two bytes data transmission. NEX13120F-Q100 only updates the PWM duty cycle of any output when its high 8-bit CONF\_PWMOUTn is written. When very fast brightness change is needed, such as fade-in and fade-out effects, it is essential to change the PWM duty cycles of all channels simultaneously. Setting CONF\_SHAREPWM to 1 enables all channels using the PWM duty cycle setting of channels 0 to save communication latency.

## **Exponential brightness control**

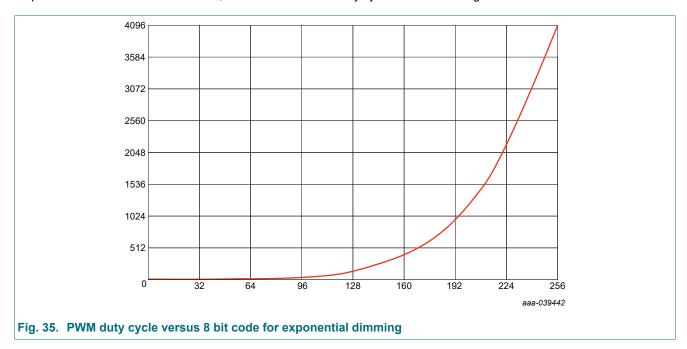

The NEX13120F-Q100 can generate PWM duty-cycle outputs that follow an exponential curve. When the CONF\_EXPEN register is set to 1, the integrated conversion circuit provides a one-to-one conversion from the 8-bit register CONF\_PWMOUTn to a 12-bit binary code that follows an exponential increment, as illustrated in <u>Fig. 35</u>. In exponential mode, the upper 8 bits (MSB) of the PWM configuration register serve as the input to the exponential conversion circuit. The output from this circuit is a 12-bit value, which is used as the duty cycle of the PWM engine.

CONF\_EXPEN bit selects the dimming method between linear or exponential. Setting the bit CONF\_EXPEN to 1 enables the conversion circuit for exponential dimming curve. In exponential PWM dimming mode, 8-bit register CONF\_PWMOUTn is converted to 12-bit PWM duty cycle by conversion circuit automatically. Clearing the bit CONF\_EXPEN to 0 disables the conversion. In this case, users must provide 12-bit PWM duty cycle. CONF\_PWMOUTn stores the high 8-bit of 12-bit PWM duty-cycle information. CONF\_PWMLOWOUTn stores the low 4-bit.

To avoid visible brightness flicker for exponential dimming, choose PWM frequency higher than 2 kHz through setting register CONF\_PWMFREQ. Higher PWM frequency can also avoid the visible LED flash in video display due to the low beat frequency between digital camera shutter frequency and PWM frequency for LED dimming.

During power-up or in Fail-Safe state, the registers CONF\_EXPEN, CONF\_PWMOUTn, CONF\_PWMFREQ are automatically reset to their default values stored in MTP register NV\_EXPEN, NV\_PWMOUTn, NV\_PWMFREQ. CONF\_PWMLOWOUTn is reset to Fh as default value.

In Fail-Safe state, PWM generator only uses 8-bit MTP data from NV\_PWMOUTn to build PWM duty cycle output and ignores the low 4-bits. The PWM duty-cycle calculation is shown in the equation below. When NV\_PWMOUTn is 00h, the channel turns off.

$$D_{OUTn} = \frac{NV\_PWMOUTn + 1}{256} \times 100\%$$

(4)

Where:

NV\_PWMOUTn is decimal number from 0 to 255 n is from 0 to 11 for different output channel

## 14.3.4. Fail-Safe state operation

The NEX13120F-Q100 supports independent channel brightness control through the UART interface. The brightness of each channel is adjustable according to its DC current register I<sub>(OUTn)</sub>, PWM duty cycle register CONF\_PWMOUTn, CONF\_PWMLOWOUTn and channel enable register CONF\_ENOUTn setting. The brightness of each channel reflects its register setting value immediately after register is successfully updated through the UART interface by master unit.

However, the master unit loses control for all current channels if the UART communication fails between the master unit and the NEX13120F-Q100. For example, the interface cable is broke, by accident. Therefore, the brightness for all output channels of the NEX13120F-Q100 is stuck and the ON and OFF control for all output channels are missing too. To keep the basic ON and OFF control for each output channel, the NEX13120F-Q100 provides a FAIL-SAFE state when the communication to master is lost. For detailed description for FAIL-SAFE state entering and quitting criteria, refer to Section 14.4. When the NEX13120F-Q100 is entering FAIL-SAFE state, all the registers are set to default value or reloaded from MTP, including CONF\_IOUTn, CONF\_PWMOUTn and CONF\_ENOUTn. The pre-programmed settings in the MTP are loaded and the corresponding registers are reset to the default values. During the MTP loading process, all the PWM output channels are disabled, and the channels' faults detected in the NORMAL state are cleared. The NEX13120F-Q100 provides one hardware input pin, FM to turn on or off corresponding current output channels in FAIL-SAFE state. Each current output channel has its own register. The FAIL-SAFE state also allows the NEX13120F-Q100 to operate as a standalone device without master controlling in the system. The FLT pin is used as a fault indicator to achieve one-fails-all-fail or one-fails-others-on diagnostics requirement. When low quiescent current in fault mode is required, the device must be set as one-fails-all-fail. In this case, if a fault is triggered, the device goes into low current fault mode.

#### 14.3.5. 8-bit ADC

NEX13120F-Q100 has integrated a successive-approximation-register (SAR) ADC for diagnostics. It routinely monitors supply voltage if the ADC is idle and stores  $V_s$  conversion results into ADC\_Vs. To manually read the voltage of an ADC channel as listed in Table 14, user must write the 5-bit register CONF\_ADCCH to select channel. Once CONF\_ADCCH register is written, the one-time ADC conversion starts and clears FLAG\_ADCDONE register. If the ADC conversion is completed, the ADC result is available in 8-bit register ADC\_OUT and sets FLAG\_ADCDONE to 1. Reading the ADC\_OUT register also clears FLAG\_ADCDONE, and the FLAG\_ADCDONE is set to 0 after reading completes. Because NEX13120F-Q100 supports PWM control for adjusting LED brightness, the voltage on OUT0 to OUT11 is like a pulse waveform. When the current output is enabled by setting CONF\_ENCHn to 1, the ADC measures the voltage on assigned OUTn after the channel is turned on with  $t_{(diag\_pulse)}$  delay time, which is programmable by 4-bit register CONF\_ODPW. When the channel is disabled by setting CONF\_ENCHn to 0, the ADC samples the voltage on assigned OUTn at off state. The analog value can be calculated based on the read back binary code with Equation 5 and Table 14. Auto scan for below values

AnalogValue =

$$a + k \times (ADC_OUT)$$

(5)

Where ADC OUT is decimal number from 0 to 255

The NEX13120F-Q100 also provides ADC auto-scan mode for single-LED short-circuit diagnostics. The detailed description for auto-scan mode can be found in <u>On-demand OFF-state single-LED short-circuit (SS) diagnostics</u>.

In ADC auto-scan mode, If MAXOUT channel is selected by writing 05h to CONF\_ADCCH, the maximum voltage of OUT0 to OUT11 is recorded into ADC\_OUT register. The maximum channel output voltage is available after at least one output PWM cycle is completed. Based on the measured maximum output voltage and supply voltage, microcontroller is able to regulate supply voltage from previous power stage to minimize the power consumption on the NEX13120F-Q100. To refresh the MAXOUT result, it is recommended to set CONF\_ADCCH to a different value before setting CONF\_ADCCH to 05 each time; MAXOUT value does not refresh, if CONF\_ADCCH remains at 05h. Basically, microcontroller needs to program the output voltage of previous power stage to be just higher than the measured maximum channel output voltage plus the required dropout voltage V<sub>(OUT\_drop)</sub> of the NEX13120F-Q100. In this way, the NEX13120F-Q100 can achieve minimum power consumption, and overall power efficiency is optimized.

**Table 14. ADC channel definition**

| CHANNEL | CONF_ADCCH | NAME     | ADC<br>CALCULATION<br>PARAMETER (a) | ADC<br>CALCULATION<br>PARAMETER (k) | Comment                        |

|---------|------------|----------|-------------------------------------|-------------------------------------|--------------------------------|

| 0       | 00h        | REF      | 0.007 V                             | 0.0101 V/LSB                        | Reference voltage              |

| 1       | 01h        | VS       | 0.0673 V                            | 0.0804 V/LSB                        | Supply voltage                 |

| 2       | 02h        | VLDO     | 0.0465V                             | 0.022 V/LSB                         | 5 V VLDO output voltage        |

| 3       | 03h        | TEMPSNS  | −242.35 °C                          | 2.152 °C/LSB                        | Internal temperature sensor    |

| 4       | 04h        | IREF     | 0.9969 μΑ                           | 0.9969 µA/LSB                       | Reference current              |

| 5       | 05h        | MAXOUT   | 0.0673 V                            | 0.0804 V/LSB                        | Maximum channel output voltage |

| 6       | 06h        | VBAT     | 0.1346 V                            | 0.1608 V/LSB                        | Vbat pin voltage               |

| 8-15    | 08h- 0Fh   | Reserved | Reserved                            | Reserved                            | Reserved                       |

| 16      | 10h        | OUT0     | 0.0673 V                            | 0.0804 V/LSB                        | Output voltage channel 0       |

| 17      | 11h        | OUT1     |                                     |                                     | Output voltage channel 1       |

| 18      | 12h        | OUT2     |                                     |                                     | Output voltage channel 2       |

| 19      | 13h        | OUT3     |                                     |                                     | Output voltage channel 3       |

| 20      | 14h        | OUT4     |                                     |                                     | Output voltage channel 4       |

| 21      | 15h        | OUT5     |                                     |                                     | Output voltage channel 5       |

| 22      | 16h        | OUT6     |                                     |                                     | Output voltage channel 6       |

| 23      | 17h        | OUT7     |                                     |                                     | Output voltage channel 7       |

| 24      | 18h        | OUT8     |                                     |                                     | Output voltage channel 8       |

| 25      | 19h        | OUT9     |                                     |                                     | Output voltage channel 9       |

| 26      | 1Ah        | OUT10    |                                     |                                     | Output voltage channel 10      |

| 27      | 1Bh        | OUT11    | 1                                   |                                     | Output voltage channel 11      |

| 28      | 1Ch        | Reserved | Reserved                            | Reserved                            | Reserved                       |

| 29      | 1Dh        | Reserved | Reserved                            | Reserved                            | Reserved                       |

| 30      | 1Eh        | Reserved | Reserved                            | Reserved                            | Reserved                       |

| 31      | 1Fh        | Reserved | Reserved                            | Reserved                            | Reserved                       |

#### 14.3.6. Diagnostic and protection in NORMAL state

The NEX13120F-Q100 has full-diagnostics coverage for supply voltage, current output, and junction temperature. In NORMAL state, the device detects all failures and reports the status out through the  $\overline{\text{FLT}}$  pin or FLAG registers, without any actions taken by the device except  $V_{BAT}$  UVLO,  $V_s$  under-voltage, and over-temperature protection. The master controller must handle all fault actions, for example, retry several times and shut down the outputs if the error still exists. The fault behavior in NORMAL state can be found in Table 17.

## V<sub>BAT</sub> and VLDO under-voltage lockout diagnostics in NORMAL state

When  $V_{BAT}$  or VLDO voltage drops below its UVLO threshold, the device enters POR state. Upon voltage recovery, the device automatically switches to INIT state with FLAG\_POR and FLAG\_ERR set to 1. The master controller can write 1 to

register CLR\_POR to clear the FLAG\_POR, write 1 to CLR\_ERR to clear FLAG\_ERR, and the CLR\_POR, CLR\_ERR bit automatically returns to 0.

## Low V<sub>s</sub>-supply warning diagnostics in NORMAL state

The NEX13120F-Q100 continuously monitors the  $V_s$  voltage and compares the results with internal threshold  $V_{(LOWVSTH)}$  set by CONF\_ADCLOWVSTH for low- $V_s$  voltage warning. If the  $V_s$  voltage is lower than threshold, the device pulls  $\overline{FLT}$  pin down with one pulsed current sink for 50 µs to report the fault and set flag registers including FLAG\_LOWVS and FLAG\_ERR to 1. The fault is latched in flag registers. When the  $V_s$  voltage rises above low- $V_s$  warning threshold, the master controller must write 1 to register CLR\_ERR to clear FLAG\_LOWVS and FLAG\_ERR. The CLR\_ERR bit automatically returns to 0. The low- $V_s$  warning is also used to disable the LED open-circuit detection and single-LED short-circuit detection. When the voltage applied on  $V_s$  pin is higher than the threshold  $V_{(LOWVSTH)}$ , the NEX13120F-Q100 enables LED open-circuit and single-LED short-circuit diagnosis. When  $V_s$  is lower than the threshold  $V_{(LOWVSTH)}$ , the device disables LED-open-circuit detection and single-LED short-circuit diagnosis. Because when  $V_s$  drops below the maximum total LED forward voltage plus required  $V_{(OUT\_drop)}$  at required current, the NEX13120F-Q100 is not able to deliver sufficient current output. The device pulls the voltage of each output channel as close as possible to the  $V_s$ . In this condition, the LED open-circuit fault or single-LED short-circuit fault can be detected and reported by mistake. Setting the low- $V_s$  warning threshold high enough can avoid the LED open-circuit and single LED short-circuit fault being detected when  $V_s$  drops to low. The  $V_{(LOWVSTH)}$  is programmable from 4 V to 19 V.

### V<sub>s</sub>-supply under-voltage diagnostics in NORMAL state

The NEX13120F-Q100 provides an internal analog comparator to monitor the  $V_s$  voltage for under-voltage protection. If the  $V_s$  voltage falls below the internal threshold,  $V_{(Vs\_th\_fall)}$ , the device pulls the  $\overline{FLT}$  pin low with constant current sink to report the fault and set flag registers including FLAG\_VSUV and FLAG\_ERR to 1. The supply under-voltage detection is used to disable all current output. When the voltage applied on the  $V_s$  pin is higher than the threshold  $V_{(Vs\_th\_rise)}$ , the NEX13120F-Q100 enables all current outputs. When  $V_s$  is lower than the threshold  $V_{(Vs\_th\_fall)}$ , the device disables every output to avoid the unwanted LED flickering or output fault triggered improperly.

The fault is latched in flag registers. When the supply voltage rises above  $V_{(Vs\_th\_rise)}$ , the master controller must write register CLR\_ERR to 1 to clear FLAG\_VSUV and FLAG\_ERR. The CLR\_ERR bit automatically returns to 0.

## Reference diagnostics in NORMAL state

NEX13120F-Q100 integrates diagnostics for REF resistor open and short fault in NORMAL state. The device monitors the reference current  $I_{(REF)}$  set by external resistor  $R_{(REF)}$ . Use Equation 6 to calculate the  $I_{(REF)}$ . If the current output from REF pin  $I_{(REF)}$  is lower than  $I_{(REF\_OPEN\_th)}$ , the reference resistor open-circuit fault is reported. The reference resistor short-circuit fault is reported if the voltage of REF pin  $V_{(REF)}$  is lower than  $V_{(REF\_SHORT\_th)}$ . The device pulls the FLT pin down with constant current sink and sets flag registers including FLAG\_REF and FLAG\_ERR to 1. The fault is latched in flag registers.

After the REF pin  $I_{(REF)}$  and  $V_{(REF\_SHORT\_th)}$  recover to normal, the device releases  $\overline{FLT}$  pin pull-down automatically and the master controller must send CLR\_ERR to clear FLAG\_REF and FLAG\_ERR. CLR\_ERR automatically returns to 0.

In NORMAL state, the device does not perform any actions automatically when reference resistor fault is detected. However, the output may not work properly, and the output current may be operating at high current level when REF short. It is recommended for master controller to shut down the device outputs and report error to upper level control system such as body control module (BCM).

The reference current  $I_{(REF)}$  is set by external resistor  $R_{(REF)}$ . The  $I_{(REF)}$  can be calculated with Equation 6.  $V_{(REF)}$  typically is 1.235V.

$$I_{(REF)} = \frac{V_{(REF)}}{R_{(REF)}}$$

(6)

#### Pre-thermal warning in NORMAL state

The NEX13120F-Q100 has pre-thermal warning at typical 135°C. When the junction temperature, T<sub>j</sub>, of NEX13120F-Q100 rises above pre-thermal warning threshold, the device reports pre-thermal warning, pull FLT pin with pulsed current sink for 50 μs and sets the flag registers including FLAG\_PRETSD and FLAG\_ERR to 1. The fault is latched in flag registers. When the junction temperature of NEX13120F-Q100 falls below pre-thermal warning threshold, the master controller must write 1

to CLR\_ERR register to clear FLAG\_PRETSD and FLAG\_ERR. The CLR\_ERR bit automatically returns to 0. When more accurate thermal measurement on LED unit is required, one current output channel can be sacrificed to provide current bias to external thermal resistor, such as PTC or NTC. The voltage of external thermal resistor can be measured by integrated ADC to acquire the temperature information of the thermal resistor located area. The master controller can determine actions based on the acquired temperature information to turn off or reduce current output.

## Over-temperature protection in NORMAL state

The NEX13120F-Q100 has over-temperature protection at  $T_{(TSD1)}$ , typical 175 °C. When device junction temperature  $T_j$  further rises above over-temperature protection threshold, the device turns off all output drivers, pulls the  $\overline{FLT}$  pin low with constant current sink to report fault, and sets the flag registers including FLAG\_TSD and FLAG\_ERR to 1. The fault is latched in flag registers. When the junction temperature falls below  $T_{(TSD1)} - T_{(TSD1\_HYS)}$ , the device resumes all outputs and releases  $\overline{FLT}$  pin pull-down. The master controller must write 1 to CLR\_ERR to clear FLAG\_TSD and FLAG\_ERR. The CLR\_ERR bit automatically returns to 0.

## Over-temperature shutdown in NORMAL state

When the  $T_j$  rises too high above  $T_{(TSD2)}$ , 180 °C typically, the NEX13120F-Q100 turns off the internal linear regulator, VLDO output to shut down all the analog and digital circuit. The  $\overline{FLT}$  pin is pulled down by constant current sink to report the fault, and the FLAG\_POR and FLAG\_ERR are all set to 1. When the  $T_j$  drops below  $T_j$  pin released. The MEX13120F-Q100 restarts from POR state with all the registers cleared to default value and  $\overline{FLT}$  pin released. The master controller must write 1 to CLR\_POR to clear both FLAG\_POR and FLAG\_ERR after fault removal. The CLR\_POR bit automatically returns to 0.

## **Communication loss diagnostic in NORMAL State**

The NEX13120F-Q100 monitors the UART interface for communication with an internal watchdog timer. Any successful non-broadcast communication with correct CRC and address matching target device automatically resets the timer. If the watchdog timer overflows, the device automatically switches to Fail-Safe state as indicated by external FM input.

- If FM = 0, the device switches to Fail-Safe state 0

- If FM = 1, the device switches to Fail-Safe state 1

The watchdog timer is programmable by 4-bit register CONF\_WDTIMER. The NEX13120F-Q100 can directly enter Fail-Safe states from normal mode by burning NV\_WDTIMER to 0xFh. Disabling the watchdog timer by setting CONF\_WDTIMER to 0x0h prevents the device from getting into Fail-Safe state.

#### LED open-circuit diagnostics in NORMAL State

The NEX13120F-Q100 integrates LED open-circuit diagnostics to allow users to monitor LED status in real time. The device monitors voltage difference between  $V_s$  and OUTn to judge if there is any open-circuit failure. The  $V_s$  voltage is also monitored in parallel with programmable threshold to determine if  $V_s$  is high enough for open-circuit diagnostics.

The open-circuit monitor is only effective during PWM-ON state with programmable minimal pulse width greater than  $t_{(ODPW)}$ . The  $t_{(ODPW)}$  is programmed by register ODPW. If PWM on-time is less than  $t_{(ODPW)}$ , the device does not report any open-circuit fault. When the device supply voltage  $V_s$  is below the threshold  $V_{(LOWVSTH)}$  set by register CONF\_ADCLOWVSTH, the LED open-circuit is not detected nor reported. When the voltage difference  $V_s - V_{(OUTn)}$  is below threshold  $V_{(OPEN\_th\_rise)}$  with duration longer than  $t_{(ODPW)}$ , and the device supply voltage  $V_s$  is above the threshold  $V_{(LOWVSTH)}$  set by register CONF\_LOWVSTH, the NEX13120F-Q100 pulls the FLT pin down with one pulsed current sink for 50  $\mu$ s to report fault and set flag registers including FLAG\_OPENCHn, FLAG\_OUT and FLAG\_ERR to 1. In NORMAL state, the device does not take any actions in response to the LED open-circuit fault and waits for the master controller to determine the protection behavior. The fault is latched in flag registers. When the voltage difference  $V_s - V_{(OUTn)}$  rises above threshold  $V_{(OPEN\_th\_rise)}$  with duration longer than  $t_{(ODPW)}$ , or the device supply voltage  $V_s$  is below the threshold  $V_{(LOWVSTH)}$ , the master controller must write 1 to CLR\_ERR to clear FLAG\_OPENCHn, FLAG\_OUT and FLAG\_ERR. The CLR\_ERR bit automatically returns to 0.

## LED short-circuit diagnostics in NORMAL state

The NEX13120F-Q100 has internal analog comparators to monitor all channel outputs with respect to a fixed threshold for reporting OUTn short to GND fault. The short-circuit detection is only effective during PWM-ON state with programmable

minimal pulse width of  $t_{(ODPW)}$ . The  $t_{(ODPW)}$  is programmable by register ODPW. If PWM on-time is less than  $t_{(ODPW)}$  the device can not report any short-circuit fault. When the voltage  $V_{(OUTn)}$  is below threshold  $V_{(SG\_th\_fall)}$  with duration longer than deglitch timer length of  $t_{(ODPW)}$ , the device pulls the FLT pin down with pulsed current sink for 50  $\mu$ s to report fault and set flag registers including FLAG\_SHORTCHn, FLAG\_OUT and FLAG\_ERR. In NORMAL state, the device does not take any actions in response to the LED short-circuit fault and waits for the master controller to determine the protection behavior. The fault is latched in flag registers. When the voltage  $V_{(OUTn)}$  rises above threshold  $V_{(SG\_th\_rise)}$  with duration longer than deglitch timer length of  $t_{(ODPW)}$ , the master controller must write 1 to CLR\_ERR to clear FLAG\_SHORTCHn, FLAG\_OUT and FLAG\_ERR. The CLR\_ERR bit automatically returns to 0.

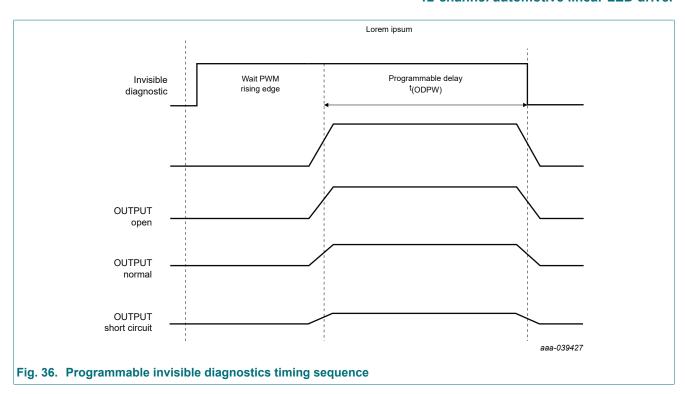

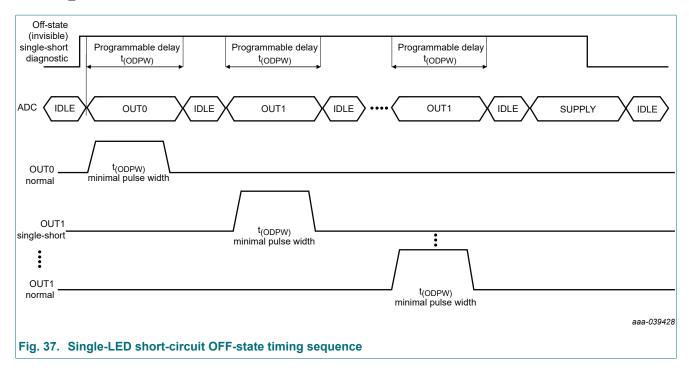

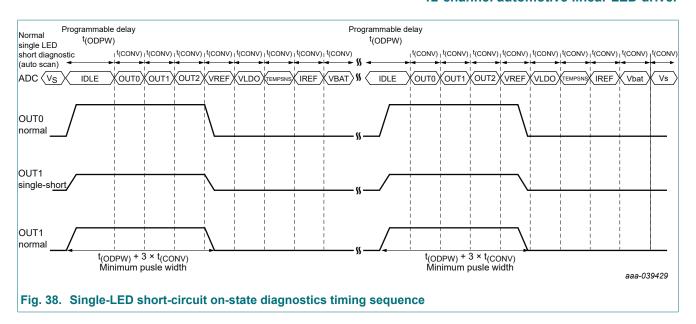

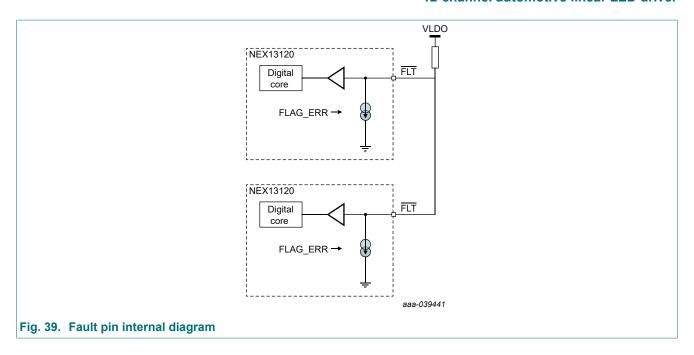

#### On-demand OFF-state invisible diagnostics